|

SPI ( Serial Peripheral Interface一一串行外设接口)总线是Motorola公司推出的一种同步串行接口技术。在原理图设计过程中,都是将主从设备对应的IO口直接连接,从来没有考虑过阻抗匹配,用了很多年,也没有出线什么问题。但是没有出现问题,不代表没有问题的。

SPI数据线要不要串联电阻进行阻抗匹配,在TI的应用文档中说到,“传言提到:总线长度只有几米,或者数据传输率很低的时候,不需要传输阻抗。请不要相信这个说法”

要不要加电阻,就要搞清楚信号传输在什么情况下,是需要进行阻抗匹配。根据传输线理论,只有当信号波长和导线长度差不多的时候,才需要考虑。传输线的效应是逐渐体现出来的。而一般的评判标准,是当导线的长度大于信号波长的十分之一到八分之一时,就需要考虑传输线效应,防止信号反射带来的波形失真。所以绝对不是只有高频,几个GHz的信号,才需要做阻抗匹配。比如模拟电话线,语音信号的带宽也就f=4KHz,但电话线系统都需要考虑阻抗匹配,比如按600欧姆或者900欧姆阻抗匹配。因为电话线是几十千米的长度,已经大于信号波长L=V/f=37km的十分之一,如果阻抗不匹配,打电话就那可能听到回声。

但数字信号就稍微复杂一些,这是由于方波信号谐波分量很多,越是陡峭的上升沿和下降沿,意味着越高的信号频率,就不能按照基波频率来计算。所以要用另一只方式来描述,就是用信号的传输时间除以信号的上升时间或下降时间,如果这个比率超过了10%,那么就需要进行阻抗匹配。

传输时间tp=L/V,其中L是导线长度,V是电磁波在电路板中的传输速度

V=C/sqrDk,其中Dk是光速衰减因子,对于电路板而言是铜线,Dk=4

电磁波在电路板中的速度都是慢于光速的。

举一个具体的例子,如果SPI的时钟信号上升时间为10ns,导线长度是15cm,这样计算下来tp/tr是大于0.1,此时就需要按照传输线设计,要进行阻抗匹配。

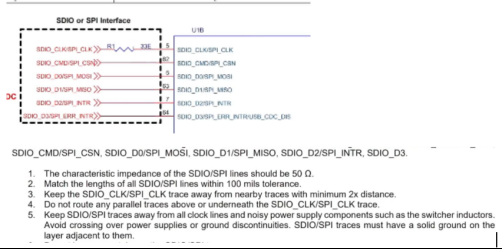

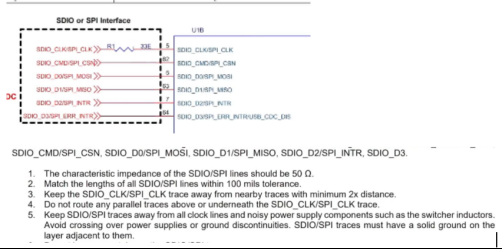

由于SPI标准没有像USB标准那样规定数据线的阻抗,这是由于SPI的通信速度不是固定的,取决于设计者和器件的极限参数,因此没有标准,也就给设计者有了很多选择。

传输线匹配的两种常见放大,就是在信号输出端串联电阻匹配,或者在接收端并联电阻匹配。在接收端并联电阻匹配的弊端:当并联电阻接地下拉或者接电源上拉时候,都会增加驱动器损耗。因此常用的方法还是前者。除此只玩,SPI的PCB设计,需要按照高速PCB布线原则来设计,确定好走线的特征阻抗,计算好走线宽度,间隔等参数。特征阻抗一般选择50欧姆或者90欧姆等等。设计好了PCB的特征阻抗,串联电阻就好选择了,一般驱动器的输出阻抗Ro在10-30欧姆之间,传输线设计的阻抗是50欧姆,那么串联的电阻Zl可以选择22欧姆或者33欧姆。Zl和输出阻抗Ro相加,就和传输线特征阻抗相等。

在一些SPI的参考设计中,比如SILICON的一款WIFI芯片RS9116,其SPI最高时钟频率达到100MHz,参考设计是在SPI通信线上面串联电阻,在layout设计中,也说明了要阻抗匹配。除了阻抗匹配,串联电阻还可以抑制振铃。

--------------------- 作者:sinasun 链接:https://bbs.21ic.com/icview-3297012-1-1.html 来源:21ic.com 此文章已获得原创/原创奖标签,著作权归21ic所有,任何人未经允许禁止转载。

|